Introduction to Samsung Electro-Mechanics package substrate

モバイルとPCの核心半導体に使われるPackage基板であり、半導体とメインボードの間の電気的信号を伝達する役割及び高価な半導体を外部ストレスから守る役割を担います。一般の基板よりはるかに微細な回路が形成されてある高密度回路基板であるため高価な半導体を直接メイン基板に装着する際に発生し得る組立不良やコストを削減することができます。

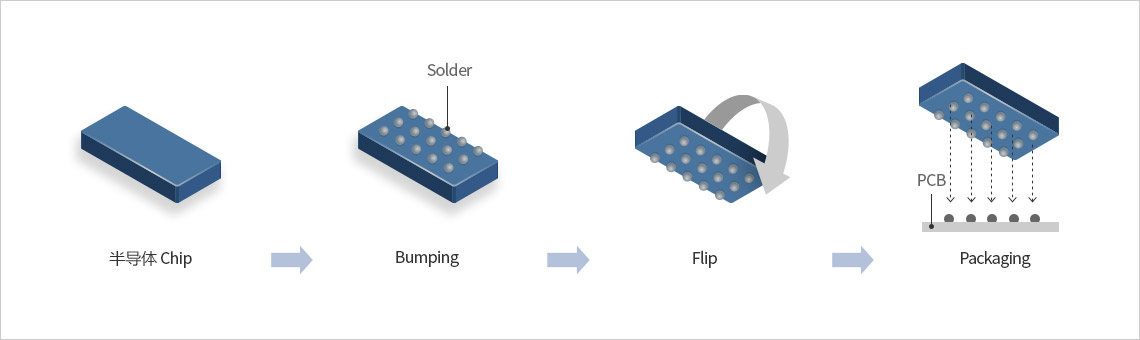

FCCSP(Flip Chip Chip Scale Package)

半導体にワイヤボンディング接合ではなくバンプを用いひっくり返したまま基板と繋ぐため、FCCSP(Flip Chip Chip Scale Package)と呼びます。主にモバイルIT機器のAP(Application Processor)半導体に使われます。また、Gold Wireを使うWBCSPと比較し電気的信号の移動経路が短く、多くの数のInput/Outputを形成できるため、高密度半導体に対応することができます。

- 適用分野

- モバイルアプリケーションプロセッサー、Baseband等

主なコア技術

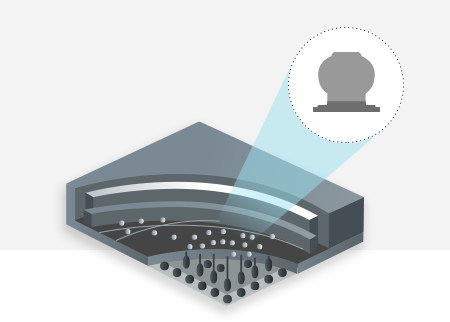

1. Bumping 構造図

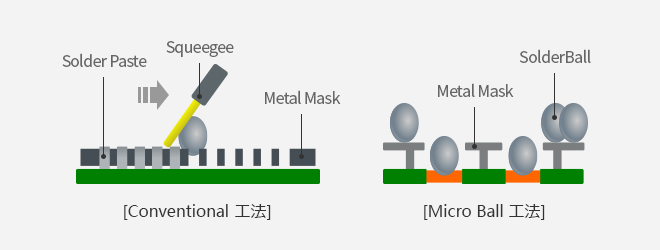

2. μBall Bump 工法

- [Conventional 工法]

- Solder Paste -> Squeegee -> Metal mask

- [Micro Ball 工法]

- MetalMask -> SolderBall

- · Available for Fine Bump Pitch

- · Good for Small Bump Risk

- · Good Quality for Bump Characteristics

基板の種類

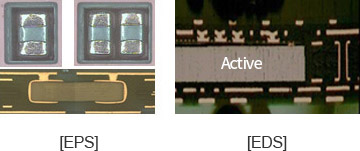

1. EPS(Embedded Passive Substrate) & EDS(Embedded Die Substrate)

EPS/EDSは半導体の受動素子、IC等を基盤の内部に内装し量産できる基板です。

Decoupling Capacitorは普通Power Supply Voltage levelを安定化するために使います。

ICを基盤内部に内装するとパッケージの大きさや厚さを縮小することができます。

2. ETS(Embedded Trace Substrate)

ETSは回路のパターンが絶縁材の中に付いている形の回路基板です。基板はCoreless構造になっており、コスト増を避け微細回路を具現でき、レイヤのダウン設計に容易(4L→3L)です。また、エッジング工程がパターンの幅に影響を与えないため、回路の幅を精密に制御することができます。

![[2Layer Buried Trace], [3Layer Buried Trace], [4Layer Buried Trace]](/resources/images/jp/product/package_img_04.jpg)

Lineup

Lineup by Specification

Mass Production Sample Available| Routing Density | Build-Up Line Width / Space | 7 / 8um (Mass Production) | 6 / 7um (Sample Available) |

|---|---|---|---|

| BVH / Pad Registration | 40 / 67um (Mass Production) | 37 / 60um (Sample Available) | |

| SRO Diameter SR Registration | 45 ± 10um (Mass Production) | 40 ± 10um (Sample Available) | |

| FC Bump Pitch (Peripheral) | 40um (Mass Production) | 35um (Sample Available) | |

| FC Bump Pitch (Area) | 90um (Mass Production) | 80um (Sample Available) | |

| Low Z-Height | Core / PPG Thickness | 40 / 18um (Mass Production) | 35 / 15um (Sample Available) |

| SR Thickness | 10 ± 4um (Mass Production) | 8 ± 3um (Sample Available) |

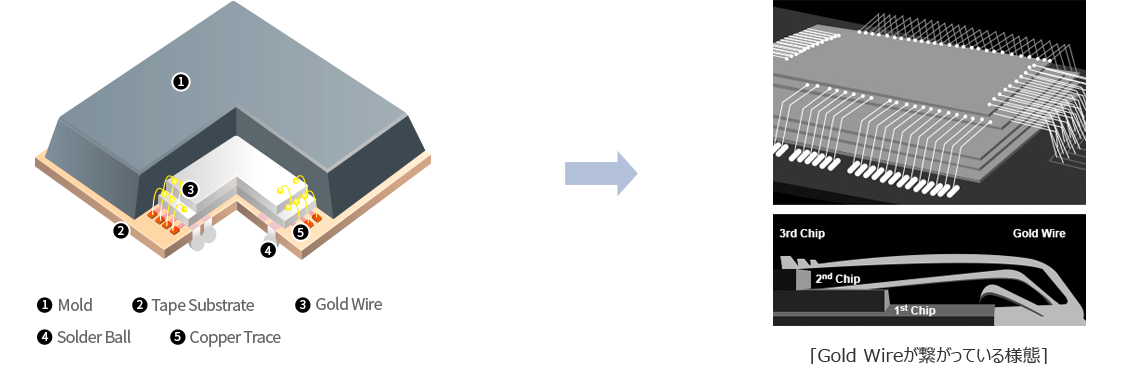

WBCSP(Wire Bonding Chip Scale Package)

Gold Wireで半導体チップとパッケージ基板が繋がっていて半導体Chipの大きさが基板面積の80%超の商品を一般的にWBCSPと言います。ChipとPCBをつなぐ際にGold Wireを利用するためマルチパッケージが可能でメモリーChipに主に使されます。特に、UTCSP(Ultra Thin CSP)商品は0.13㎜以下の厚さで商品を製作することが可能で、Chip to PCB Connectionが自由であるため、Multi Chip Packagingが可能で、同一の厚さのPackageと比べ高性能のものを具現できます。

- 適用分野

- モバイル向けメモリーチップ

- 1. Mold

- 2. Tape Substrate

- 3. Gold Wire

- 4. Solder Ball

- 5. Copper Trace

- [Gold Wireが繋がっている様態]

Lineup

Lineup by Specification

| Routing Density | Bond Finger Pitch | 55P (25 / 12, Ni 3) (Mass Production) | 50P (20 / 10, Ni 2) (Sample Available) | |

|---|---|---|---|---|

| Line Width / Space | mSAP (Cu T 14) |

12 / 16um(Mass Production) | 10 / 15um(Sample Available) | |

| ETS (Cu T 13) |

7 / 8um (Mass Production) | 6 / 7um (Sample Available) | ||

| Via / Pad Size | mSAP | 50 / 90um(Mass Production) | 45 / 85um(Sample Available) | |

| ETS | 40 / 65um (Mass Production) | 37 / 60um (Sample Available) | ||

| SRO alignment | ± 12.5um (Mass Production) | ± 10um (Sample Available) | ||

| Min. SR Open size | 45um (Mass Production) | 40um (Sample Available) | ||

Lineup by Structure & Z-Height

Mass Production Sample Available| Layer count | Structure | Thickness | |

|---|---|---|---|

| 2Layer (Mass Production) | Cored (Mass Production) | 80um (Mass Production) | 75um |

| 3Layer (Mass Production) | Coreless (Mass Production) | 80um (Mass Production) | 75um |

| ETS (Mass Production) | 120um (Mass Production) | 100um | |

| 4Layer (Mass Production) | Cored (Mass Production) | 120um (Mass Production) | 110um |

| Coreless (Mass Production) | 110um (Mass Production) | 100um | |

| ETS (Mass Production) | 160um (Mass Production) | 140um | |

| 6Layer (Mass Production) | Cored (Mass Production) | 220um (Mass Production) | 180um |

| Coreless (Mass Production) | 200um (Mass Production) | 180um | |

SiP(System in Package)

Packageの中に複数のICやPassive Componentが実装されており、複合的な機能を一つのSystemに具現してくれる商品です。また、PA(Power Amplifier)のような商品に使われ、防熱の特性があります。商品シリーズとしてはFlip-Chip SiPやCorelessがあります。

- 適用分野

- PA(Power Amplifier)、PAMID (Power Amplifier Module with Integrated Duplexer)、FEMID(Front-End Module with Integrated Duplexer)、

SAW Filter、BAW Filter、Diversity FEM、Switch等各種RF部品

特徴

1. 小型化

複数のIC及び受動素子が一つのModuleに統合されPackageになっており小型化を実現してくれます。

![[SiP 構成の様態]](/resources/images/jp/product/package_img_06.jpg)

- 1. Sip

- 2. Die 1

- 3. Die 2

- 4. Die 3

2. 薄板の具現

超薄板の駆動性を確保することで0.2mmの厚さの基板(6層基準)を具現できます。

, [ 0.27T 8L RF-SiP ](270um), [ 10L ~、5G アンテナモジュール ]](/resources/images/jp/product/package_img_07.jpg)

主なコア技術

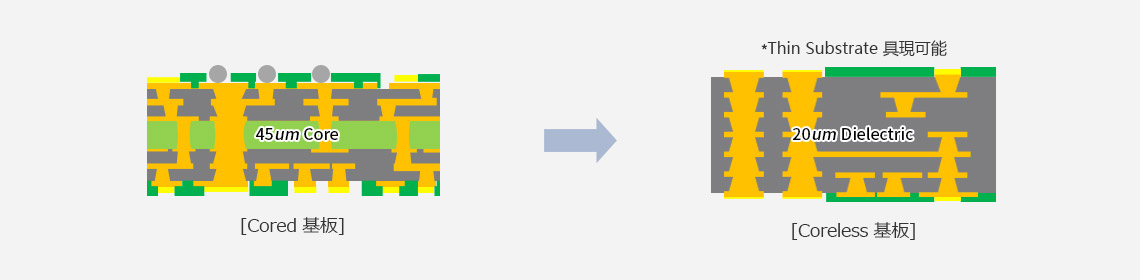

1. Coreless RF-SiP

Coreless工法で絶縁の厚さを縮小、EMI(Electro Magnetic Interference)及びParasitic Inductanceをコントロール、信号の特性を向上させることができるため、これを基にThin Substrateを具現できます。

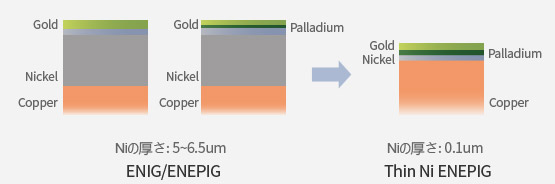

2. ENEPIGの表面処理

ENEPIGの表面処理技術は下記のような特性があります。

-

1) Thin Ni ENEPIG

- Bonding PadのNiの厚さを減少させRFの特性を改善

- Gold, Nickel, Copper, Palladium

- Ni Thickness: 5~6.5um ENIG/ENEPIG

- Gold, Nickel, Palladium, Copper

- Ni Thickness: 0.1um Thin Ni ENEPIG

* ENIG : Electroless Nickel Immersion Gold

* ENEPIG : Electroless Nickel Electroless Palladium Immersion Gold -

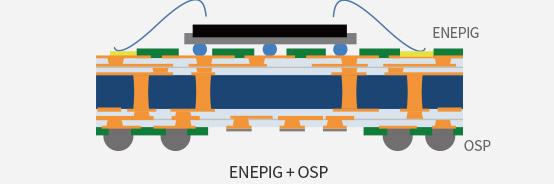

2) Selective ENEPIG

- 同一の面内での異種表面処理が可能(ENEPIG + OSP)

- Lorem Ipsum, ENEPIG, OSP

- ENEPIG + OSP

* OSP : Organic Solderability Preservative

Lineup

Lineup by Specification

Mass Production Sample Available| Layer Structure | Cored | 2L / 4L / 6L / 8L / 10L (Mass Production) | + 12L / 14L (Sample Available) |

|---|---|---|---|

| Coreless | 5L / 6L / 7L / 8L (Mass Production) | + 4L / 9L / 10L (Sample Available) | |

| Line Width / Space | 12 / 16um (Mass Production) | 10 / 15um (Sample Available) | |

| Bump Pitch | 130um (Mass Production) | 105um (Sample Available) | |

| Surface Finish | Direct Au, Thin ENEPIG, Selective ENEPIG (Mass Production) | Direct Au, Thin ENEPIG, Selective ENEPIG (Sample Available) | |

FCBGA(Flip Chip Ball Grid Array)

高集積半導体チップをマザーボードと接続するための高密度パッケージ基板です。半導体チップとパッケージ基板をフリップチップのバンプで接続し、基盤回路の微細化及び高多層に伴う層間微細整合が求められ、特にハイパフォーマンスコンピューティングに対応するため、大型ボディサイズ、高多層(~75x75㎜、20L)技術を要します。

- 適用分野

- CPU, GPU, Server CPU, AI Accelerator, Automotive, Network, Game Console, D-TV

![FCBGA(Flip Chip Ball Grid Array) [1.Solder Ball, 2.Solder Bump, 3.Pattern, 4.Chip]](/resources/images/jp/product/package_img_11.jpg?ver=240216)

Lineup

FCBには、Standard CoreとThin Core商品があります。

Mass Production Sample Available| Core Thickness (um) | Line Width/Space Bump Pitch (Mass Volume) |

Layer Counts | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 4L | 6L | 8L | 10L | 12L | 14L | 16L | 18L | 20L | 22L | |||

| Standard Core | 1200 | 9 / 12um 90um |

Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Sample Available |

| 800 | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Sample Available | ||

| 600 | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | ||||

| 400 | Mass Production | Mass Production | Mass Production | Mass Production | Mass Production | Sample Available | ||||||

| Thin Core | 250 | 9 / 12um 100um |

Mass Production | Mass Production | Mass Production | Mass Production | Sample Available | |||||

| 200 | Mass Production | Mass Production | Mass Production | Sample Available | ||||||||

| 150 | Mass Production | Mass Production | Sample Available | |||||||||